As Communications Service Providers (CSPs) worldwide scale up the deployments of their 5G networks, they face strong pressure to optimize their Return on Investment (RoI), given the massive expenses they already incurred to acquire spectrum as well as the ongoing costs of infrastructure rollouts.

QSFP-DD, the new ‘kid’ on the block

In continuation of my previous blog – “Flexible Pluggable Front Port Technology”, the current blog focuses on the latest addition to the QSFPx form factor family – the QSFP-DD.

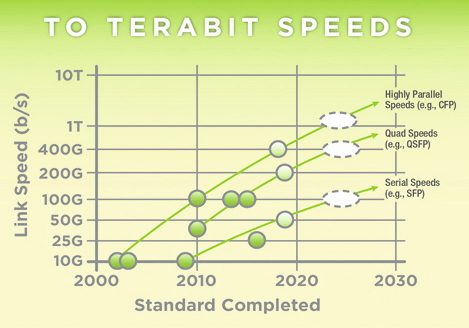

Ethernet Roadmap Speed Tracks

The Ethernet roadmap distinguishes between the following 3 speed tracks, see Figure 1:

- Highly Parallel Speeds (1st track)

- Quad Speeds (2nd track)

- Serial Speeds (3rd track)

The technological evolution usually enables a transition through the 3 tracks, as shown in the picture above, for a given link speed/type over a given period of time (see case study below).

100GBASE-LR4 Case Study

- Introduction on 1st track: In 2009 the 100GBASE-LR4 standard was introduced in the “Highly Parallel Speeds” track, supported by the CFP formfactor. The CFP module houses the gearbox function, enabling mapping between the four 25Gbps lanes on the optical side, and the ten 10Gbps lanes on the host side, as seen in Figure 2. In 2012, the same functionality was introduced in the smaller CFP2 formfactor.

- Transition on to the 2nd track: In 2013, the 100GBASE-LR4 standard was introduced in the “Quad Speeds” track, supported by the CFP2 formfactor without gearbox functionality between the host and the optical side. The same functionality was in 2015 introduced in the smaller CFP4 formfactor, and in 2016 in the even smaller QSFP28 formfactor.

- Transition on to the 3rd track: The technological evolution is expected to enable the introduction of a single-lane product in the “Serial Speeds” track in the mid-twenties, completing the described transition process.

Backward Compatibility and shared form factors between speed tracks

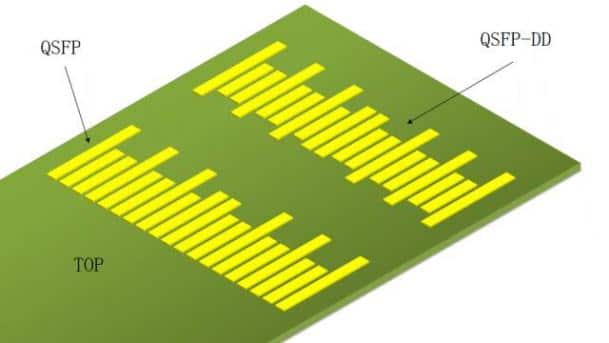

The CFP2 form factor was introduced as a dense successor to the CFP. As mentioned in the 100GBASE-LR4 case study above, the CFP2 form factor supports both the CAUI-10 and the CAUI-4 host side interface, making it the first form factor to span two speed tracks in the Ethernet roadmap, the “Highly Parallel Speeds”- and the “Quad Speeds” track. Being a new form factor, the CFP2 however didn’t do well in terms of backward compatibility with existing link speeds. The newly introduced QSFP-DD form factor spans the same two-speed tracks, but is additionally also backward compatible in the “Quad Speeds” track with previous QSFP standards, QSFP+ and QSFP28. Backward compatibility is enabled by a brilliant doubling of the supported number of host interface lanes through a 2nd row of contacts in the module interface, as seen in Figure 3.

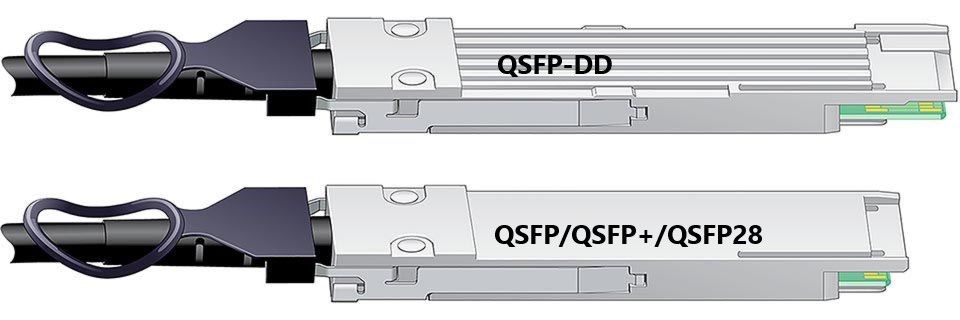

The extra contact row on the QSFP-DD pluggable module calls for a more advanced counterpart connector, housed in the QSFP-DD cage. When a QSFP+ or QSFP28 module is inserted, it only connects to the first contact row, see Figure 4. One of the few downsides of the QSFP-DD standard is the extra PCB real estate required by the advanced QSFP-DD connector.

The future for the QSFP-DD Form factor

The future looks very bright for the QSFP-DD form factor. It has been introduced as one out of many competitors in the 400G form factor arena, but has already gained significant momentum with respect to competition, CFP8 and OSFP. All major optical module manufactures, including AOI- and DAC cable manufactures are working on roadmap products supporting the new QSFP-DD form factor. Momentum has been gained through the described key technical offerings but not unimportantly also through support from several data center operators, including Facebook who has announced that the QSFP-DD form factor is their preferred choice for new installations.