Leveraging Napatech’s industry-proven hardware, Link-Programmable™ provides OEMs and end users with a solid platform for deploying their own custom FPGA computation solutions.

Open Standard Servers

Peak performance at minimal cost

Ethernet Front Port Compliance

Error-free uninterrupted operation

Event Handling & System Monitoring

Seamless integration – maximized uptime

Thermal Performance

Optimized rack-space utilization

Regulatory Compliance

Quick integration with no delays

Shock & Vibration Robustness

Strong resilience to rough environments

PCI Compliance

Proven uncompromising quality

Rivaling clustered HPC at a fraction of the cost

Link-Programmable™ brings massive parallel processing capacity to compute intensive applications. The hardware is designed to accommodate thermal and slot-size constraints, enabling 8+ cards to sit adjacent in a single COTS server. Through ultra-highspeed interconnects, the cards can distribute workloads across FPGAs, providing parallel processing capacity comparable to clustered high performance computing (HPC) solutions at a fraction of the cost.

Powered by Xilinx UltraScale+ FPGA

FPGA solutions for compute acceleration can enable up to 90x higher performance compared to CPUs, and over 4x higher inference throughput than GPU-based solutions.

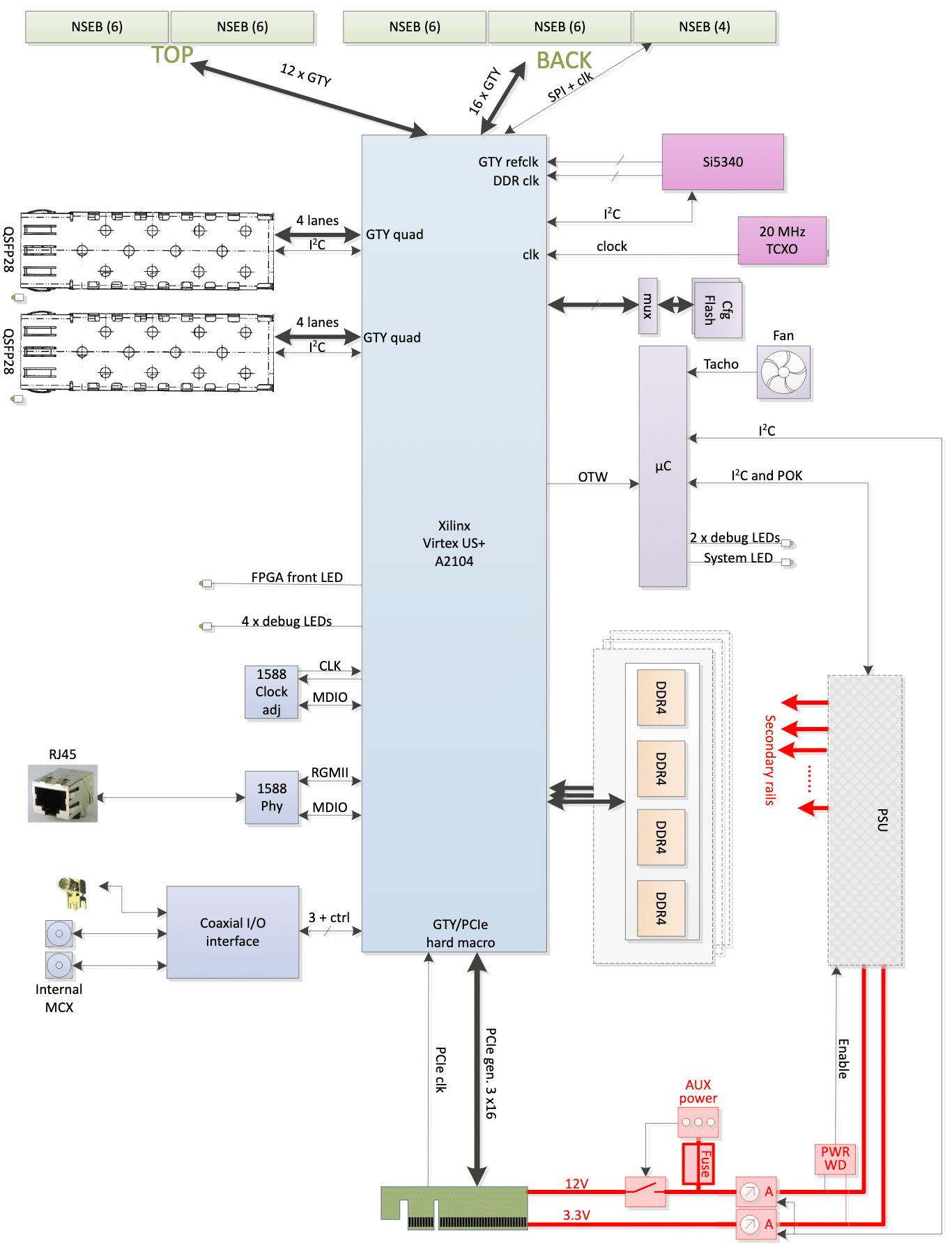

Built on the Xilinx 16nm UltraScale+™ architecture, the Link-Programmable™ flagship card pushes the Xilinx 3rd generation FPGA to its maximum, enabling highest signal processing and serial I/O bandwidth to satisfy the most demanding design requirements.

Link-Programmable™ is ideal for compute intensive applications ranging from 1+ terabit/second networking, computer vision, ultra-low latency high-frequency trading to cryptocoin mining.

The platform is fully supported by the Xilinx Vivado® design suite for rapid prototyping and product maturing. It is flexible and can be configured with various types of memory banks and FPGA chips, e.g. XCVU7P or XCVU9P.

Ruggedized and industry-proven hardware

Meticulously designed, validated and compliance-tested to minimize integration risks in the server environment, Link-Programmable™ enables OEMs and end users to focus their efforts on the target application, removing complexity and uncertainty from the integration process.

With ~300,000 hours of mean time between failures (MTBF), our hardware ensures uninterrupted,

error-free operation for many years ahead – as validated by our long-term loyal customer base.

Link-Programmable™ Development Kit

The Development Kit is available for the Link-Programmable™ family, containing:

• Interface cables necessary to program the hardware using a Xilinx Vivado® Probe

• A comprehensive hardware manual

• Xilinx Vivado® pinout files

• Xilinx example design images (PCIe, QSFP, DDR)

Through the Xilinx Vivado® design suite, FPGA developers can use a mix of Verilog/VHDL, C, C++ or SystemC for faster path to IP creation. Read more at Xilinx Vivado®

Napatech NT200A02 features:

To generate and control the airflow, the Napatech design contains a blower that takes in air from the top and bottom of the card, thereby doubling the amount of air and ensuring superior cooling.

Benefits

- Durable design for extended real-life operation

- Free choice of server platform

- Reduced noise and power-consumption as server-fans can run at minimum speed

- Freedom to pack unlimited FPGA SmartNICs into a standard server

Specs

- No airflow dependency to server

- Well-defined cooling of all critical components

- Guaranteed device hot spot temperatures

- Maximized airflow, ensuring optimal thermal performance

- Dissipated energy exhaled outside server through front plate cutouts

- Significant reduction in temperature drop between FPGA die and heat sink surface

- Mechanical stiffener enabling higher screw torque for fastening heatsink to the PCB

Compliance

Napatech upholds the highest quality, environmental and safety standards, and complies with all applicable regulations across regions. This helps our customers to realize a seamless integration without delays – and ensures error-free operation throughout the product life cycle.

Ethernet Front Port Compliance

All Napatech designs maximize mechanical and electrical front port margin, securing trouble-free operation with the optical or electrical modules of the customer’s choice.

The thermal design is validated dissipating the maximum power level as standardized for the given form factor. Margin on the data interface has been optimized tuning the equalization parameters of the transceivers hosting the front port channel, maximizing EYE margin to the relevant standard.

EMC Compliance

All Napatech designs have passed EMC compliance testing for major regions, including Europe and North America. By ensuring compliance as an integral part of the design, the risk of delays is eliminated. Moreover, the EMC testing has been performed in a mainstream server, potentially directly applicable to the use case.

Environmental Compliance

The end product must adhere to regional environmental legislation. To enable trouble-free server integration, Napatech hardware is manufactured using only materials that fully comply with the current RoHS, REACH and proprietary Tier 1 legislation.

Full compliance from early inception eliminates the risk delays and product withdrawal due to authority intervention.

Event Handling & System Monitoring

To become an integral part of the server environment and maximize uptime, the hardware needs to monitor and expose key performance metrics to the application during operation. Napatech hardware monitors the following metrics:

- Blower speed

- Hot spot temperatures

- Key supply voltages and currents

- PCI protocol events

- General system events

PCI Compliance

With the PCI interface dictated by the server plane, the hardware maximizes mechanical and electrical PCI margin, ensuring trouble-free operation in the server and server slot(s) of the customer’s choice. All designs have passed relevant PCI-SIG tests and have been adopted on the PCI-SIG integrators list.

Safety Compliance

To enable trouble-free server integration, Napatech hardware is fully compliant with all applicable safety standards.

By ensuring safety compliance as an integral part of the SmartNIC design, the risk of delays is eliminated. Compliance testing is performed in a mainstream server, potentially directly applicable to the use case.

Conflict Minerals Compliance

To ensure quick and trouble-free server integration, Napatech hardware is manufactured using only materials that fully comply with the relevant Conflict Mineral Legislation. For US based integrators, this facilitates submission of the mandatory Conflict Mineral report to SEC.

Shock & Vibration Robustness

Many server environments expose the card to substantial shock and vibration, predominantly during the transportation phase. To ensure trouble-free server integration and operational robustness throughout the product life cycle, validated design aspects include:

- Cooling enclosure for superior mechanical stiffness

- Key exposed components are under-filled (glued) to the PCB

- Shock robustness validated against JESD22-B110A

- Vibration robustness validated against ASTM D4169-09

Diagram

Flagship tech specs

| TECH SPECS | NT200A02 SmartNIC |

| Form factor | Half length, full height PCIe |

| Front ports | 2 x QSFP28 front ports supporting 1, 10, 25, 40, 50, 100 GbE |

| FPGA | Xilinx Ultrascale+, XCVU5P-2FLGA2104E On demand: • XCVU7P-2FLVA2104E • XCVU9P-2FLVA2104E Optional: Speed Grade 1 or 3 |

| Configuration flash | 2 banks of 1 Gbit, 4 bit wide (QSPI) |

| Memory | 3 x DDR4 banks of 64 bit @ 2666 Mbps, total: 12 GB Optional: 24 GB using 16 Gbit devices |

| PCIe | x16 Gen3 Optional: 2 x 8 Gen4 below PCIe spec v0.7 (1) |

| 1000Base-T port | RJ45 front port connected to 1 Gb PHY with full SyncE and IEEE 1588v2 capabilities |

| Single ended coaxial I/O | Front port SMA connector and 2 internal MCX connectors |

| High-speed interconnect port | Interconnect bidirectional bandwidth of 675 Gb/s with Napatech interconnect cable Top: 2 x high-speed interconnect ports with 6 lanes each Optional: Back: 3 x high-speed interconnect ports; 2 with 6 lanes each and 1 with 4 lanes + SPI, 12V and clock |

| Power consumption | HW design: 120 W UL compliant with NIM to 75 W Idle: 5 W |

| Reference clock | 20 MHz TCXO +/- 4.6 ppm Optional: 20 MHz OCXO +/- 0.01 ppm |

| Board microcontroller | ATxmega128A1U |

| Hardware board monitoring | Temperature and power sensors |

(1) For detailed information regarding limitation on PCIe Gen4 support in Xilinx UltraScale+, please contact Xilinx.

Applications ideal for FPGA processing

Based on Xilinx UltraScale+ FPGAs, Link-Programmable™ is ideally suited for anything compute intensive and can be deployed across a variety of industries and applications.

High Efficiency Video Coding

Cryptomining

Machine Learning

High Frequency Trading

Analytics

| Audio/Video | DSP, Speech recognition, HiRes video, computer vision |

| Broadcast | RealTime video, Encoders, EdgeQAM, Switching/Routing |

| Data Center | Switching/Routing/Load balancing, Virtualization, Highspeed |

| High Performance Computing | Data mining, AI Inference, Big Data analysis |

| Integrated Circuit Design | ASIC prototyping, HW emulation |

| Financial | Crypto Mining, High Frequency Trading |

| Medical | CT Scan, MRI, X-Ray, PET, Ultrasound |

| Security | Image processing, industrial imaging, Crypto, Authentication |